# HEWLETT-PACKARD JOURNAL

Technical Information from the Laboratories of Hewlett-Packard Company

#### JULY 1983 Volume 34 • Number 7

#### **Contents:**

**A High-Speed System for AC Parametric Digital Hardware Analysis,** by Andreas Wilbs and Klaus-Peter Behrens Here's a 50-MHz multichannel stimulus/response system for test-ing digital circuits at realistic speeds.

A High-Speed Data Generator for Digital Testing, by Ulrich Hübner, Werner Berkel, Heinz Nüssle, and Josef Becker It offers high timing accuracy, precise pulse-level definition, ease of operation, and versatility.

High-Speed Data Analyzer Tests Threshold and Timing Parameters, by Dieter Kible, Bernhard Roth, Martin Dietze, and Ulrich Schöttmer Two innovative features are programmable sampling point delay and real-time compare mode.

**Data Analyzer Software/Firmware Design, by Roberto Mottola and Eckhard Paul** A skilled task dispatcher makes full use of the interrupt structure of the CPU.

**Power Supplies for the Stimulus/Response System, by Ulrich Otto and Horst Link** The objectives were high load current and serviceability within a restricted space.

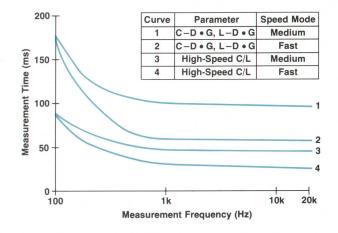

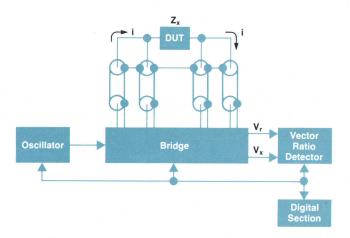

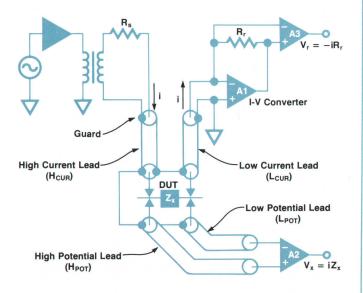

**32 New Multi-Frequency LCZ Meters Offer Higher-Speed Impedance Measurements,** by **Tomio Wakasugi, Takeshi Kyo, and Toshio Tamamura** These new instruments can be easily combined with a component handler for more rapid production-line testing.

Authors

#### In this Issue:

Quality is high on everyone's priority list these days, and one of the principal paths to quality is testing, thorough and realistic, at all phases of the process of designing and producing a product. This month's issue deals with two families of test instruments that are aimed at assuring the quality of the myriad diodes, transistors, resistors, capacitors, inductors, integrated circuits, circuit boards, and modules that go into electronic equipment. Each family has a target range of testing applications and a repertoire of special capabilities needed in those applications.

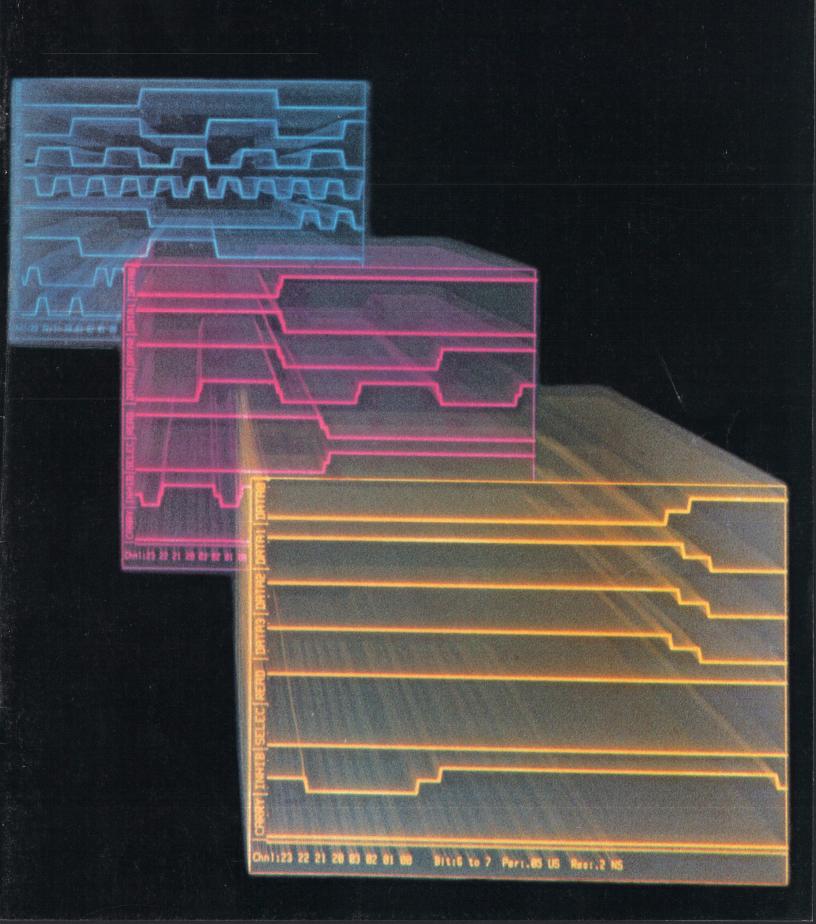

On this month's cover are three views, at progressively finer resolution, of the timing diagram of a RAM (an integrated circuit random-access memory chip). Memory circuits like this one, along with microprocessors, gate arrays, and other digital integrated circuits (ICs) are becoming faster and more complex at a startling rate—sometimes the next generation is announced before its predecessor is in production. The system that produced this timing diagram is designed to keep up with the rapidly changing state of the art and to test fast, complex digital ICs at realistic speeds and in minute detail. This family of instruments, consisting of the 8180A Data Generator, the 8181A Extender, and the 8182A Data Analyzer, is distinguished by a time resolution of 100 picoseconds (there are a million picoseconds in a millionth of a second) and the analyzer's programmable sampling point delay. These features make it possible to zero in on the briefest of IC events. You can read all about the design of this system on pages 3 to 31.

While the 8180A/81A/82A System is designed for relatively low-volume testing of complex, high-performance digital ICs in engineering, quality assurance, depot maintenance, and certain kinds of incoming inspection and production testing of discrete components (LCZ stands for inductance-capacitance-impedance). They also have their uses in the engineering laboratory and in semiconductor evaluation. By testing components faster and more realistically than previously available equipment, these instruments improve the quality and lower the cost of the products we purchase. Fed by an automatic component handler (available from several manufacturers), they'll check up to ten components per second and sort them into as many as ten classes, and keep it up hour after hour without attention. For reporting test data, they're compatible with computers and plotters, and for realistic testing, they offer a variety of test frequencies and voltages. The designers tell their story on pages 32 to 38.

-R.P. Dolan

Editor, Richard P. Dolan

Associate Editor, Kenneth A. Shaw

Art Director, Photographer, Arvid A. Danielson

Illustrators, Nancy S. Vanderbloom, Susan E. Wright

Administrative Services, Typography, Anne S. LoPresti, Susan E. Wright

European Production Supervisor, Henk Van Lammeren

# A High-Speed System for AC Parametric Digital Hardware Analysis

This new 50-MHz stimulus-response system is a state-of-the-art tool for comprehensive and rapid characterization of all types of digital circuits.

#### by Andreas Wilbs and Klaus-Peter Behrens

R APIDLY ADVANCING SEMICONDUCTOR technology now makes it possible to integrate thousands of functions on a single chip, making digital circuits increasingly more complex. They are also getting faster. Subnanosecond propagation delays per gate are already feasible, allowing clock rates of 50 MHz and higher even for complex devices. Furthermore, new circuit designs, both custom and semicustom (gate arrays), are receiving broad acceptance in the marketplace.

This evolution has changed the requirements for digital test equipment. The most significant new requirements are: Higher data rates and more channels

- More accurate timing and stimulus/comparator levels

- A capability for longer test patterns.

It is also important for instrumentation to be compact, quick to set up, and adaptable to different devices and measurement problems.

Traditional measurement solutions do not fulfill these new requirements. Big expensive test systems, for example,

are well suited to dc parametric tests and provide high production throughput, but for low-volume engineering applications, they are seldom readily available, and most are too slow for testing fast devices at speed. The lack of a live keyboard and difficult operating and programming procedures make such systems inflexible and prevent the quick access necessary in a laboratory environment. Another traditional solution is the self-configured, dedicated setup containing several word/pulse generators for stimulus, and logic analyzers, counters, and oscilloscopes for analysis. Programming these different instruments requires long familiarization, and synchronizing the setup is difficult and time-consuming.

#### **The New Solution**

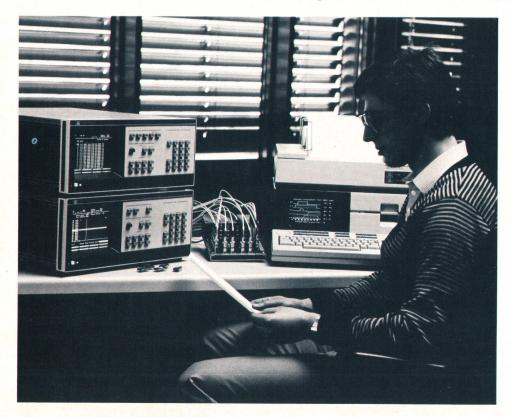

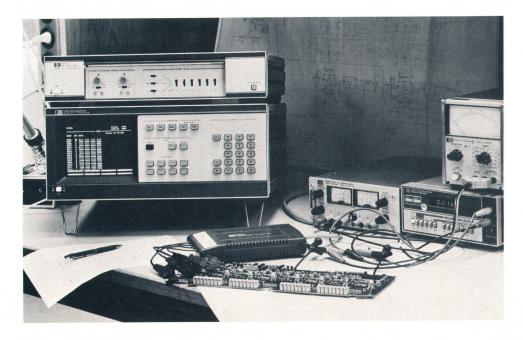

The new HP 8180A/81A/82A Stimulus/Response System (Fig. 1) provides an answer to the new requirements. It offers both device stimulation and response analysis, and consists of the 8180A Data Generator, the 8181A Extender,

Fig. 1. The 8180A Data Generator (top left), the 8181A Extender (not shown), and the 8182A Data Analyzer (bottom left) provide high-performance, easy-to-use, economical at-speed testing for digital integrated circuits, boards, and modules. The system can be controlled by a desktop computer (right) via the HP-IB (IEEE 488).

### Parametric Characterization of Digital Circuits

The representative timing parameters of synchronous ICs are setup time, hold time, and propagation delays. During the setup and hold times, data has to be stable before or after an active clock transition occurs. The propagation delay is the time between stimulation and the output reaction of a device. This value depends upon the complexity of the circuit and its technology, and varies from less than 1 ns for an ECL gate to over 100 ns for an MOS gate. Hence, the measuring instrument must have high timing resolution. In addition, these timing parameters depend on the dynamic input characteristic of a device. For example, the reaction time of a comparator depends on the input overdrive.

At the output of the device under test, the variation of amplitude with frequency is of interest. A driver may have the ability to deliver adequate dc current under the specified fanout conditions, but be unable to deliver adequate peak current to drive the parasitic capacitance at high clock rates.

#### Applications of the New System

The 8180A/81A/82A System is oriented predominantly towards the solving of engineering measurement problems. IC and board designers need to measure parameters to specify the performance and optimize the yield of ICs, or achieve a high turn-on rate of boards. Digital IC manufacturers do parametric characterization of ICs in the prototype phase, allowing the process to be optimized. They also use parametric analysis to establish sales specifications and for in-depth evaluation in the quality assurance department.

The 8180A/81A/82A System's main applications for digital circuit, module, and system manufacturers are found in R&D, production engineering, quality assurance, incoming inspection, and materials engineering. For example, various propagation delays must be matched for minimum skew. Logic functions must be verified. A stimulus is required to simulate the interface pattern of a board that is not yet built. Parametric circuit test at the board level has the same requirements and objectives as at the IC level, differing in complexity and error sources. The cross talk on a bus with parallel lines or data stability during the time window around the system's synchronous clock are of interest. Other applications include low-volume and at-speed testing in production, incoming inspection, and depot maintenance, where traditional equipment such as board testers offers insufficient speed and timing performance. High-reliability applications, such as aerospace equipment, also demand a 100% parametric test in addition to detection of soldering and component loading errors. Component approval and production engineering departments are also application areas for the new system.

which expands the number of stimulus channels, and the 8182A Data Analyzer. Each of the units can be configured for different numbers of channels. In addition, provision has been made for the synchronous operation of two systems in parallel. This expands the channel count with a minimum of skew. Generator/analyzer synchronization and interaction with the device under test are assured by various control inputs and outputs. Adaptability and clean signals are provided by a range of useful accessories. Although the instruments are designed as a system and offer the same key specifications, the 8180A (with or without the 8181A) and the 8182A can also be operated individually. Each unit has its own control processor, display, keyboard, and HP-IB (IEEE 488) interface. This modular concept makes the instruments very adaptable to different devices and measurement problems.

This compact system brings the performance of a big tester to the bench. Its user-oriented softkey operating concept speeds the setup of timing and level parameters, either manually or under HP-IB control. The same is true for test pattern creation, which is further simplified by standard data patterns and pattern editing features.

Modularity gives the user the means to adapt a system exactly to requirements, thus keeping the cost low enough to justify the expense. This is important in low-volume testing, where the return from high throughput found in production areas is not achieved.

The need for high speed is satisfied by the system's 50-MHz data rate. This is faster than most of the big IC testers and covers most applications, bearing in mind that the overall speed of a device is much slower than a single gate delay. The rate slows with increasing complexity, so that even fast ECL devices can be tested by the system. In addition to a fast rate, sophisticated timing capabilities are provided for setting up various test patterns for an IC. The stimulus channels provide independent delay and data width programming, with excellent resolution of 100 ps for very tight adjustments. Operation of the 8182A Data Analyzer is mostly synchronous, a technique similar to that employed by more expensive IC test systems. It is capable of both synchronous (external clock) and asynchronous (internal clock) operation, and it also offers 100-ps resolution, never previously achieved in an asynchronous analyzer. When the device under test and the analyzer are synchronized, automatic comparison of sampled data with expected data is possible. The 8182A's threshold level range is sufficiently wide to test all common logic families, and logic levels are independently adjustable for mixed logic circuits. The level resolution is 10 mV.

#### **Data Generator Provides Stimulus**

The 8180A Data Generator outputs a digital data pattern according to the user's specifications, which may include data rate, bits per word, number of data words, levels, timing relationships between channels, and other parameters. The data generator contains the following basic blocks:

- Timing circuits to achieve specific timing relationships between channels

- Memory to hold the data pattern that is to be output in parallel

- Output amplifiers that determine the output voltage swings

- Control inputs and outputs

- Central processor unit

- HP-IB interface

- Keyboard and display.

An add-on unit and pods provide for three-state operation with programmable levels for testing bidirectional buses.

The 8180A is designed to be the stimulus for parametric

hardware analysis. Therefore, it provides precise level and timing capabilities at high speed. This is in contrast to other types of word generators, which often provide data patterns only at low speed, with moderate or no level definition and poor timing capabilities.

The 8180A can be configured as an 8-to-16-channel generator in 4-channel increments. A maximum of eight channels can be RZ (return to zero), that is, having independently programmable delay and width. All other channels are NRZ (non return to zero) channels. The channel count can be expanded by using up to two 8181A Extenders, each with a maximum of 24 NRZ channels with programmable common delay. This configuration provides 64 channels. Synchronous parallel operation doubles this number to 128.

#### **Data Analyzer Measures Response**

The 8182A Data Analyzer collects, analyzes, and displays digital bit patterns. These tasks are performed according to the user's specifications, which may include input thresholds, data qualification, sampling point (the point in time at which data is sampled, referenced to the external clock), compare time window, and other parameters. The 8182A contains the following basic blocks:

- Input comparators to determine the states of logic signals

(1, 0, or between high and low thresholds)

- Trigger circuits to indicate the beginning or end of data capture

- High-speed memory to store sampled data

- Low-speed memory to hold reference data

- Timing circuits to determine precisely when data is to be captured or compared

- Control inputs and outputs

- Central processor unit

- HP-IB interface

- Keyboard and display.

The 8182A Data Analyzer is designed for high-speed functional and parametric hardware analysis of digital circuits. The data analyzer can be configured from 8 to 32 channels in 8-channel increments, each channel having identical analyzing capabilities. Synchronous parallel operation doubles the number of channels to a maximum of 64.

#### **User-Friendly Operation**

The 8180A Data Generator and 8182A Data Analyzer are designed to fulfill the requirements of digital circuit hardware analysis. For this reason the usual data generator and logic analyzer concepts have been replaced by a new operating concept tailored to this application. The design goals for this new concept were:

- Fast, guided setup of the instrument, thereby dispensing with the operating manual in a relatively short time

- Parameter changing during the instrument's active state (live keyboard)

- Comfortable data loading, edit, and display features

- Simple HP-IB programmability for fast program generation

- Similar operation of both instruments.

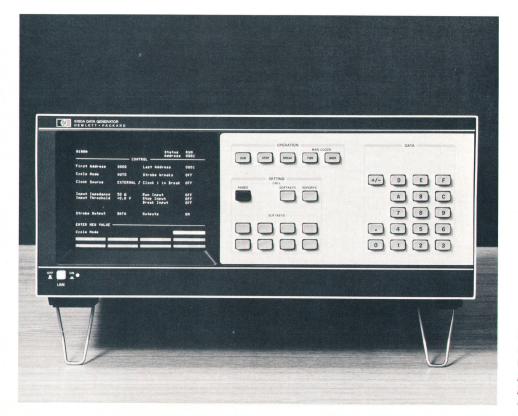

To reduce the number of keys and the confusing use of shift keys, a layered menu softkey concept was chosen. The display is divided into three areas (see Fig. 2). The top of the screen next to the **OPERATION** keys gives status information. (These keys operate independently of all other keys on the front panel). The remainder of the display is split into a report area, showing one of seven selectable reports

**Fig. 2.** The 8180A Data Generator and the 8182A Data Analyzer have similar operating concepts, displays, and front panels. The display is divided into status, report, and softkey areas.

(parameter settings or data display), and the softkey area containing the entry field, which shows the selected parameter and the labels for the eight softkeys beside the screen. Softkey and report areas can be selected independently or in common by the **CALL** keys. If the entry field is not activated, the area can be used to extend the data display in the report area. The parameters are selected by the softkeys either directly (e.g., softkey label Cycle Mode to access the cycle mode), or through a softkey tree (e.g., softkeys Trigger and Delay lead to trigger delay). After selection, the parameters can be changed either by softkeys or by data keys. Any softkeys that contribute nothing to the current operational status of the instrument are blanked to avoid confusing the user.

This operating concept offers quick access to every parameter, regardless of the contents of the report area.

#### **Similar Operation**

The 8180A Data Generator and 8182A Data Analyzer are designed to operate similarly, so that a user who is familiar with one instrument can use the other without a long familiarization time. The keyboards differ in only three keys. Softkeys with the same function for each instrument are labeled identically and occupy the same position on both keyboards (many softkey label sets on both instruments are identical). The pages displayed are very similar, too, with main settings shown on the control page. The timing parameters, which appear on the analyzer's control page, require a page of their own in the generator. The generator's output page corresponds to the analyzer's input page in the same way the 8180A output data page corresponds to the 8182A expected data page.

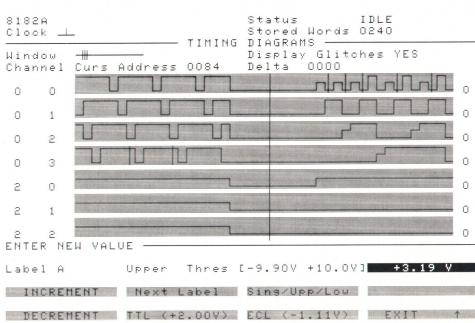

Both instruments have a miscellaneous page, which in the 8182A also contains store and recall functions. A special feature of the generator is the macro data page, which extends considerably the editing capabilities of the instrument. The data analyzer has three pages on which to display received data in the form of the state list, the timing diagram, and an entirely new feature called the error map. The error map gives a concise overview of the Compare Data result. It displays one dot for each memory location. This dot is replaced by a square if data received differs from expected data. Furthermore, there are special features for the individual masking of any bit or word (see article, page 14).

The expected data page, the state list, and the data page in the 8182A are user-defined. Channels can be deleted from the display or grouped together in segments of up to 16. The channels in each segment can be configured in a manner that is totally independent of their hardware order, enabling the user to assign a code to every segment. It is also possible to display a channel in more than one segment concurrently. The timing diagram offers a full set of features, such as zooming in both horizontal and vertical axes, glitch display, delta measurement, and individual channel arranging.

Special attention was paid to the editing features. The 8180A has memory, line, and channel editing features. Memory editing consists of set and clear functions. Channel editing provides clear, set, counter, PRBS (pseudorandom binary sequence), and copy. Line editing functions include insert, delete, copy, and move. It is also possible to define a set of 16 words (macros) on a special page, and then copy one or more of them to the data memory.

In addition to many of the above features, the 8182A has other analyzer-oriented editing features for expected data. These include the setting and clearing of masks, and the ability to copy received data to the expected data memory for future comparison.

#### Live Keyboard

For fast parametric measurement it is often necessary to change instrument parameters during the measurement phase. In the 8180A this is achieved by changing all analog parameters without disturbing the generator output in any way. If other changes (e.g., output data) are being made, the instrument interrupts the cycle to make the change, and then returns to the point at which the cycle was interrupted.

Fig. 3. When changing measurement parameters during a measurement, the display can be split into two areas, one of which shows control page parameters in the softkey area. Here the timing page is displayed while the probe threshold is being changed. This operation is performed without disturbing clocks or data. Therefore, the device under test, which contains only combinational and sequential logic, does not recognize the interruption.

The 8182A Data Analyzer's input thresholds can also be changed during the active cycle (data capture). Other analyzer features facilitate fast measurements. The microprocessor displays the received data not only when the instrument stops, but also when the data rate falls below 10 MHz. This is a particularly useful attribute when dealing with slow clock rates or clock bursts. Other instruments usually have to abort a measurement to display the data received. Another useful feature is auto-arming. This allows the user to preselect the point in time at which the instrument will begin a new measurement, so that the result of any change in the operating condition of the device under test can be displayed immediately.

To ensure that the instrument is operable during a period of processor activity, the keyboard is interrupt-controlled, permitting the storage of up to eight keystrokes until the processor has time to respond to them. When changing measurement parameters during a measurement phase, it is possible to split the display screen into two areas, one showing the report area (perhaps the error map), and the other showing control page parameters in the softkey area. Fig. 3 shows an example; the timing page is displayed while the probe threshold is being changed. The HP-IB system is designed to give direct access to parameters and a fast instrument response. The mnemonics are easy to remember, avoiding the need to refer to the manual continuously, making programming simple and reducing familiarization time. To program the 8180A to a frequency of 20 MHz, for example, the controller sends the message FRQ 20 MHZ. Where the parameters on each instrument are identical, so are the mnemonics.

For the transfer of high volumes of data from the controller to the instrument and vice-versa, a binary transfer mode has been implemented. In this mode, every byte on the bus is dedicated to eight bits of data. Data transfer rates of 12,000 bytes per second are achieved, giving a data reload time of less than two seconds for the whole system. This makes it possible to write fast-running programs.

#### Acknowledgments

We would like to thank Roberto Mottola for his outstanding contribution in defining the operating concept for both instruments, Horst Link, who was responsible for the mechanical design of all instruments and accessories, Eckhard Hettlage, who designed the displays, Peter Stollenmaier, who contributed to the 8182A power supply, Rainer Storn, who helped with the 8182A self-test software, and last but not least, our thanks go to Günter Riebesell and Reinhard Falke for their help and guidance along the way.

# A High-Speed Data Generator for Digital Testing

by Ulrich Hübner, Werner Berkel, Heinz Nüssle, and Josef Becker

HE NEW HP 8180A DATA GENERATOR represents a significant step forward in the production of highspeed data generators. It offers high timing accuracy, precise pulse-level definition, ease of operation with either manual or remote control, and great flexibility on the bench and in the rack.

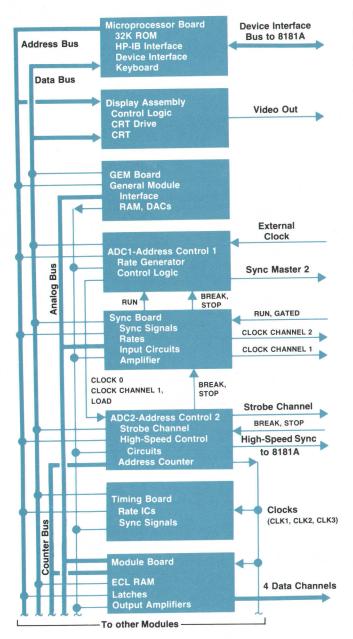

The 8180A consists of a power supply module, a display module, and eleven printed circuit boards, which plug into a motherboard. Fig. 1 illustrates the various functional blocks and main interconnections.

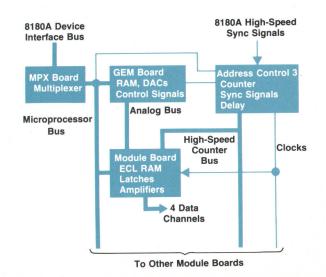

The 8181A Data Generator Extender is constructed along the same lines as the 8180A with the exception of the display and keyboard. All control functions are performed by the 8180A, the 8181A being merely a system slave. Fig. 2 is a block diagram of the 8181A.

#### Internal System Organization

All high-speed control signals in the 8180A Data Generator are generated on two boards, designated Address Control 1 and Address Control 2 (ADC1 and ADC2). The logic consists of 10k and 100k ECL devices and is controlled by the central processing unit by way of a high-speed bidirectional bus.

On ADC1, three signals that synchronize the address counters and signals for both clock channels are generated. The board responds to the commands RUN, GATED, STOP, and BREAK. There are three basic operating modes:

- Single cycle: a RUN signal starts a single cycle from the preset first address to the preset last address.

- Auto cycle: after a RUN signal, data is generated repetitively from the first to the last addresses.

- Initialization and auto cycle: a RUN signal starts data generation at address 0000. Data generation continues to the first address and then cycles between the first and last addresses repetitively.

In these three operating modes, cycling is halted on receipt of a BREAK or STOP signal.

Two further modes are controlled from this board:

Fig. 1. Block diagram of the 8180A Data Generator.

- Gated cycle: a gate signal at the external RUN input causes data generation for as long as the input remains true. If the input goes false, the currently active cycle is completed.

- Initialization and gated cycle: operation is similar to the initialization and auto cycle mode. The currently active cycle is always completed when the gate input goes false.

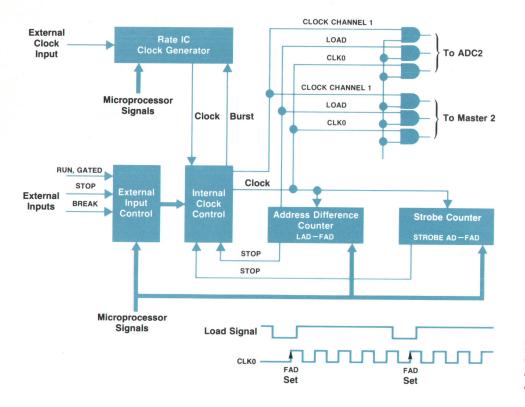

- In either mode, cycling ceases on receipt of a STOP signal. Fig. 3 is a functional block diagram of ADC1. The basis of

all internal timing circuits is the Rate IC. This specially developed device is used in recent HP pulse, function, and data generators.<sup>1</sup> Features of the Rate IC include a programmable oscillator with a range of 1 Hz to 100 MHz, programmable delay with a range of one second to 10 ns, and resolution of 100 ps or three digits when programmed by the microprocessor via a 10-bit DAC (digital-to-analog converter). Decade counters for ranging are built into the chip. The Rate IC generates the system clock in both internal and external clock modes.

Another important feature of ADC1 is the address difference counter. This 10-bit presettable counter operates continually in the count-down mode, counting clock pulses. Each clock pulse corresponds to an address. Whenever the LOAD signal goes low (Fig. 3), indicating a counter state of all zeros, the counter is preset to the difference between the first and last addresses programmed by the user. LOAD then goes high and the counter counts down until it again reaches a state of all zeros. LOAD then goes low and the cycle repeats.

A break at a defined address is performed by the strobe counter. This device is loaded by the microprocessor with the break address minus the first address.

The internal clock control generates two high-speed signals, CLK0 and CLOCK CHANNEL 1. These and the LOAD signal control and synchronize all other high-speed circuits in the 8180A and 8181A. By bypassing these signals, it is possible to set up a master-master system with two 8180As operating in parallel. In this case, only one instrument is active. The LOAD, CLK0, and CLOCK CHANNEL 1 signals are fed via a rear connector directly into the second 8180A. Bypassing is achieved automatically when the interconnecting cable is fitted.

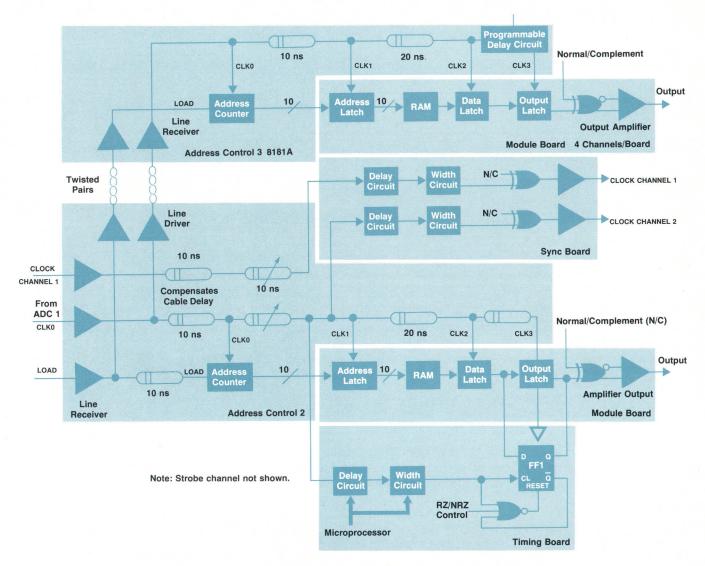

Fig. 4 illustrates the principal signal paths on the ADC2 board. Signals CLK0, CLOCK CHANNEL 1, and LOAD are fed from ADC1 to ADC2 on twisted-pair lines by line drivers. Line receivers pick up these differentially transmitted signals, refresh them, and drive the delay lines. Another line driver generates the differential signals for the 8181A Extender. The CLK0 and LOAD signals are fed to the 8180A's address counter delayed by 10 ns to compensate for the delay introduced by the interconnecting cable to the 8181A.

The address counters support all data channels in the 8180A and 8181A. Several delay lines are required to achieve correct timing relationships with the module boards that carry the data channels (four channels per

Fig. 2. Block diagram of the 8181 A Data Generator Extender.

**Fig. 3.** The Address Control 1 circuit generates synchronizing signals for the various 8180A operating modes.

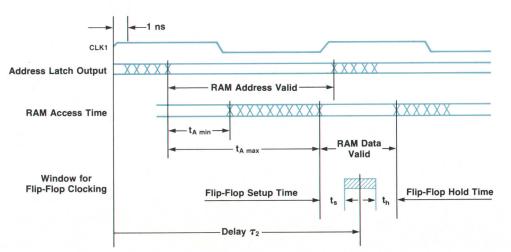

board). One delay line generates the signal CLK1, which guarantees sufficient setup time for the address latch. Fig. 5 shows worst-case conditions for high-speed RAM operation.

CLK2, delayed by 20 ns, latches the RAM's output data. This data then passes to the output latch after a further 10-ns delay, and finally to the XOR gate at the output amplifier input. The extra delay is necessary for generating RZ data when the instrument has been fitted with an additional timing board. Data from the data latch is fed to the reset flip-flop FF1 where, dependent upon delay and width settings, it is clocked through to the Q output. The negativegoing edge resets the flip-flop in the RZ mode via the OR gate, and the XOR gate at the input to the output amplifier switches between normal and complementary operation.

In the 8181A the timing circuits on the ADC3 board are very similar to those described above. The main difference is in the programmable delay, which makes it possible to compensate for delay variations between the 8181A NRZ and 8180A data channels. The programmable delay is also needed for setting up address and data buses that differ in timing.

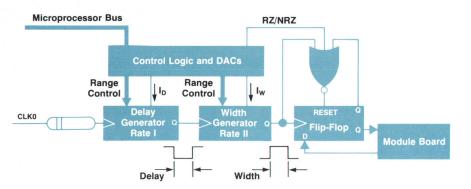

#### **Timing Board**

The timing board consists of four delay and width generator channels. At the heart of each channel is the Rate IC,<sup>1</sup>which in this application is configured to function in its timing mode. The use of conventional devices instead of Rate ICs would have taken about five times the space to achieve the same objective.

Fig. 6 shows the basic blocks of a timing channel. Inaccuracies in analog voltages generated by the DACs and peripheral components necessitate a number of control current adjustments to achieve an optimal overlap of ranges and the matching of clock inputs. The control for ranging and current programming comes from microprocessor commands sent along the bus. The function of the reset flip-flop is described in the preceding section. 32 adjustments are necessary to set up a timing board for operation, eight for each channel. Repeatability and stability results are excellent because of noncritical design and well specified components.

#### **Module Board**

The module board consists of four data channels implemented with high-speed ECL RAMs, latches for timing, and an output amplifier for each channel. With the exception of the output amplifiers, no setup or adjustments are necessary on this board. This facilitates the addition of extra boards to the 8180A or 8181A with a minimum of inconvenience. The layout of each functionally identical channel is designed in such a way that compensation for skew, introduced by the different cable lengths attached to the rear connector, is achieved by striplines on the board.

A module board complete with cables and rear connector can be fitted or replaced merely by removing two screws from the instrument's rear panel and taking off the cover. Each channel on the module board is individually screened to avoid EMI problems from neighboring channels, and to provide a heat sink for the transistors in its output amplifier.

#### Sync Board

The sync board consists of two clock channels, CLOCK CHANNEL 1 and CLOCK CHANNEL 2. Both channels have DACs for delay and width programming and use the same output amplifiers as the module boards. For applications that require refresh capability, CLOCK CHANNEL 1 is kept

Fig. 4. 8180A/8181A timing and signal distribution.

**Fig. 5.** The delayed clock signal CLK1 guarantees sufficient setup time for the address latch under worst-case high-speed operating conditions.

running in STOP or BREAK; hence it is handled differently from CLOCK CHANNEL 2.

# **Fig. 6.** The timing board consists of four delay and width generator channels (one shown).

#### **Output Amplifier**

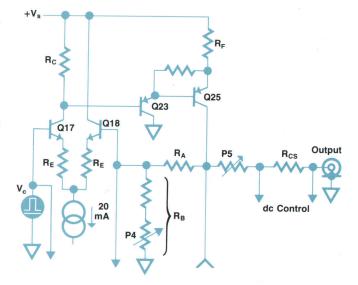

The final circuit in every data and clock channel is the output amplifier. It is here that timing information (highlow transitions) and dc voltages to program the high and low levels are translated into the desired pulse stream at the output. The functional diagram, Fig. 7, shows the amplifier's four major blocks. The first two form a pulse generator, and the last two a linear power amplifier.

Timing information in the form of switching commands is applied in a symmetrical ECL logic format at inputs Q and  $\overline{Q}$ . The signal is amplified by symmetrical complementary differential amplifiers, which control current sources in a cascade arrangement. The outputs of the four switched current generators are combined to form a pair of alternating bidirectional current sources, which drive a diode clamping bridge at nodes  $V_c$  and  $\overline{V_c}$ .

The clamp voltages  $V_c$  and  $\overline{V}_c$  are held equal to either the upper or lower programmed voltage by unity-gain buffers U1a and U1b. In the Q=high state, the symbolic DPDT switch takes the position shown in Fig. 7. Positive current flows through D4 into the lower voltage follower U1b, and negative current through D1 into the upper voltage follower

**Fig. 7.** Output amplifier block diagram. The output amplifier translates timing information and dc voltages into the desired pulse stream at the output pods. The first two blocks form a pulse generator and the last two a linear power amplifier.

U1a. As long as  $\rm V_{HI}{>}V_{LO}$  with at least 0.5V difference, D3 and D2 may be regarded as switched off.

Two more diodes, D5 and D6, compensate for the on voltages and temperature dependence of D3 and D4. All diodes are supplied with equal currents ( $I_c$ =15 mA). Minor differences in forward voltage drop and series resistance of the matched pairs D3, D5 and D4, D6 are corrected by trimmers. Thus V<sub>c</sub> is equal to exactly ½V<sub>HI</sub> when D4 is conducting (Q=high), and ½V<sub>LO</sub> when D3 is conducting. A small error because of junction temperature differences remains in D3 and D4 when they are switched on or off. Schottky-barrier diodes are chosen for fast switching without storage delay.

The second clamping node,  $\overline{V}_c$ , provides a complementary pulse train to  $V_c$ . This is used for two dynamic purposes. To accelerate the high-low transitions of  $V_c$ ,  $\overline{V}_c$  is high-pass coupled to the bases of switched current-source transistors. The result of this additional drive is that the voltage transitions of  $V_c$  are more like pulses with constant rise time than the natural constant-slope behavior of a current-steered voltage clamp.

The second purpose of the  $\overline{V}_c$  branch is to provide constant current loading for voltage-followers U1a and U1b. If D1 and D2 were not present, these op-amps would be required to deliver pulsed output currents. Frequency response limitations within the op-amps would lead to duty-cycle-dependent level variations in some critical high-frequency regions. The symmetrical clamping bridge draws dc current from U1a and U1b, keeping pulse tops flat from dc to the nanosecond region.

The clamp output signal  $V_c$  is amplified to the desired amplitude and power by a class-A push-pull amplifier. In Fig. 8, only the upper half of the amplifier, with components determining gain  $A_o$  and output impedance  $Z_o$ , is shown. The complementary symmetrical lower branch completes the amplifier for dc operation, and acts as a doubler for overall transconductance and output current. This basic arrangement is noninverting.

Minor aberrations and tolerances are trimmed out with

|                                                        | Table I                                                                                                                           |                                                                                                                                                      |  |  |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Data Generato                                          | or Output Amplifier                                                                                                               | Performance                                                                                                                                          |  |  |

| Programmed load<br>condition                           |                                                                                                                                   | from 50Ω into high<br>impedance (≥10 kΩ)                                                                                                             |  |  |

| High level range                                       | -1.5V to +5.5V                                                                                                                    | -1.0V to +17.0V                                                                                                                                      |  |  |

| Low level range                                        | -2.0V to $+5.0V$                                                                                                                  | -2.0V to $+16.0V$                                                                                                                                    |  |  |

| Resolution                                             | 3 digits (best case<br>10 mV)                                                                                                     | 3 digits (best case<br>20 mV)                                                                                                                        |  |  |

| Amplitude range                                        | 0.5V to 5.5V                                                                                                                      | 1.0V to 17.0V                                                                                                                                        |  |  |

| Level accuracy after                                   | <b>20 ns settling time</b><br>±0.5% of level<br>±3% of amplitude<br>±30 mV (add<br>±30 mV<br>for amplitudes<br>>0.7V)             | 40 ns settling time<br>$\pm 0.5\%$ of level<br>$\pm 3\%$ of amplitude<br>$\pm 30 \text{ mV}$ (add<br>$\pm 30 \text{ mV}$<br>for amplitudes<br>>1.5V) |  |  |

| Level accuracy after                                   | 1 ms settling time<br>$\pm 0.5\%$ of level<br>$\pm 30 \text{ mV}$<br>(add $\pm 30 \text{ mV}$ for<br>amplitudes $< 0.7\text{V}$ ) | 1 ms settling time<br>$\pm 0.5\%$ of level<br>$\pm 60 \text{ mV}$<br>(add $\pm 60 \text{ mV}$ for<br>amplitudes $< 1.5\text{V}$ )                    |  |  |

| Transition time (10%-90%)                              | <3.0 ns +<br> amplitude ×0.2 ns                                                                                                   | <3.0 ns +<br> amplitude ×0.5 ns                                                                                                                      |  |  |

| Typical transition<br>time for ECL levels<br>(20%-80%) | 1.5 ns                                                                                                                            | _                                                                                                                                                    |  |  |

| Preshoot, Over-<br>shoot, Ringing                      | $<\pm10\%$ of amplitude                                                                                                           | e <±10% of amplitude                                                                                                                                 |  |  |

Table I

P4, for the amplifier unloaded, and again with P5, after connection of a  $50\Omega$  load.

Output amplifiers commonly found in pulse and data generators are usually designed as current or voltage sources, both needing an internal 50 $\Omega$  load to present the

Fig. 9. The tri-state pod makes the data generator outputs compatible with bidirectional bus and I/O pin configurations. The control and power unit on top of the 8180A Data Generator is part of the pod system. correct  $Z_o$  (50 $\Omega$ ) at their output. The amplifier concept used here gives well-defined gain and output impedance without wasting 50% of the ac power on an internal 50 $\Omega$  ballast. This is important in generators in which many data channels are packed closely together, like the 8180A and 8181A.

Internal feedback in every amplifier stage  $(R_E, R_F)$  helps ensure stability and allows the use of full circuit speed (speed is ultimately limited by the propagation delay around the feedback loop in the amplifier network). The free-running amplifier produces an output signal with the specified accuracy. A dc offset of up to several hundred millivolts reflecting the thermal history of linearly operating transistors may appear, however. A dc error can also be introduced by varying the supply voltages to accommodate different output amplitude requirements. To eliminate these offsets, an additional dc control loop checks the output voltage and the output current simultaneously and ensures precise operation under any loading, level, or supply conditions.

To understand the operation of this dc control loop, look at the inputs of error amplifier U2 in Fig. 7. At the noninverting input, a voltage  $V^+ = \frac{1}{2}(V_o + R_{CS}I_o)$  is compared with  $V^- = \frac{1}{2}V_c + \frac{3}{6}V_o$  at the inverting input. The op-amp forces a corrective current into the inverting input of the main amplifier to keep  $V^+ - V^- = 0$ . The dc precision now depends on the op-amp quality and the ratio of the resistors in the voltage divider. When  $V^+ - V^- = 0$ , then  $V_o + R_{CS}I_o = V_c + \frac{3}{4}V_o$ . Since  $A_o = 4$  and  $R_{CS} = 50\Omega/A_o$ , this expression

becomes  $\frac{1}{4}V_o + (50 \Omega/A_o)I_o = V_c$ , or  $V_o = A_oV_c - (50 \Omega)I_o$ , which describes a linear amplifier with voltage gain  $A_o$  and an output impedance of  $50\Omega$ .

Table I shows the principal specifications of the output amplifier.

#### **Tri-State Pod**

The tri-state pod is an accessory to the 8180A Data Generator and 8181A Extender. Its function is to make the generator outputs compatible with bidirectional bus and I/O pin configurations.

The main design aims for the tri-state pod were to be able to output any level in the generator's output range of -2V to +5.5V, and to function as an analog switch, enabling the control of different logic families. At the same time, the level programmability of the system had to be maintained. Other objectives were fast switching, high output impedance with low capacitance in the off state, and low output impedance with high drive capabilities in the on state, giving high speed when driving high-capacitance loads.

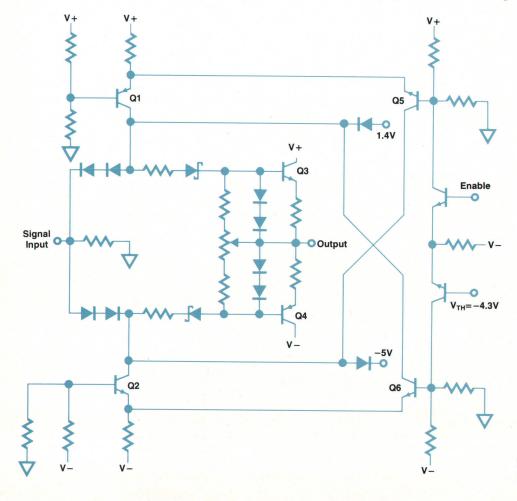

The solution adopted uses the familiar diode bridge (Fig. 9). A disadvantage is that the power consumption of the bridge reduces the ratio of output to input currents significantly. This problem was solved by a complementary transistor stage that reduces the bridge supply current.

In the left-hand side of the bridge, two pairs of series diodes produce a drop of approximately 1.4V. This is always greater than the drop across the Schottky diode and

**Fig. 10.** Schematic diagram of the tri-state driver.

the emitter junction of the output transistor in each line. The series Schottky-diode-resistor configuration, in combination with an offset adjustment, permits the use of unmatched components without a reduction in level accuracy. When the enable voltage meets or rises above the -4.30V threshold, transistors Q5 and Q6 begin to conduct, thereby turning Q1 and Q2 off. In this way, the bridge becomes reverse-biased, with the clamping diodes ensuring that the output circuit is cut off when the voltage at the output is in the range -2V to +5.5V.

#### Reference

1. C. Hentschel, et al, "Designing Bipolar Integrated Circuits for a Pulse/Function Generator Family," Hewlett-Packard Journal, Vol. 34, no. 6, June 1983.

# High-Speed Data Analyzer Tests Threshold and Timing Parameters

by Dieter Kible, Bernhard Roth, Martin Dietze, and Ulrich Schöttmer

ONVENTIONAL DATA ANALY ZERS fall generally into two categories. First, there are the high-speed asynchronous timing analyzers, which produce test results similar to an oscilloscope on several channels. These analyzers are used mainly for functional analysis of random logic. Second, there are the synchronous state analyzers, which are used mostly for the functional analysis of microprocessor-based systems with real-time or other complex sequential logic. Parametric measurements, on the other hand, have to be made with oscilloscopes or timing analyzers having fairly coarse time resolution (the fastest timing analyzers available offer only 1.5 to 2 ns resolution, with a significant additional error because of skew between data channels).

The new 8182A Data Analyzer is optimized for testing threshold and timing parameters at high speeds. It has two innovative features—programmable sampling-point delay and real-time compare mode. New, specially-developed active probes with a wide range of accessories facilitate the capture of data with minimum influence on the device under test. All analog parameters, such as threshold voltages and the sampling point delay, are implemented with high resolution and accuracy. Instead of setup and hold times, a sampling time accuracy with respect to the external clock input is specified. This is more suitable for parametric measurements of integrated circuits and printed circuit boards.

The 8182A is controlled by a 6809 processor with 40K bytes of ROM space and a 14K CMOS RAM that is battery-powered for nonvolatile data storage. All I/O interfacing is memory-mapped to achieve fast access to all parameter registers.

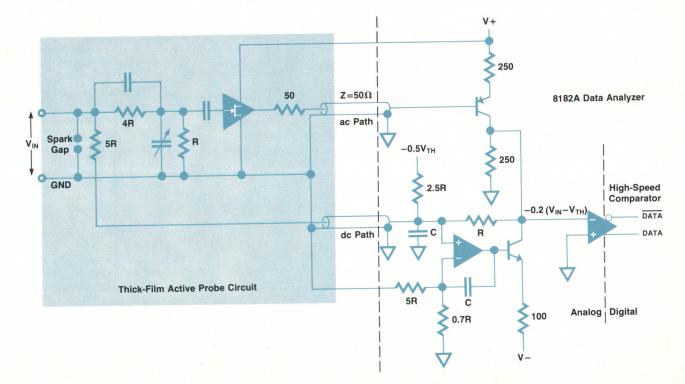

#### **Three Operating Modes**

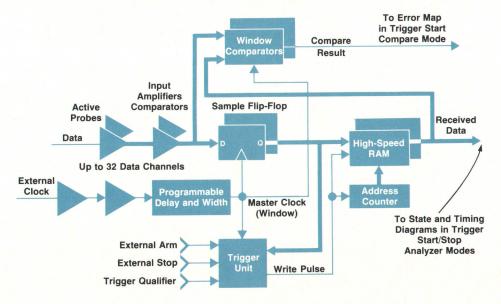

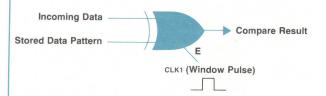

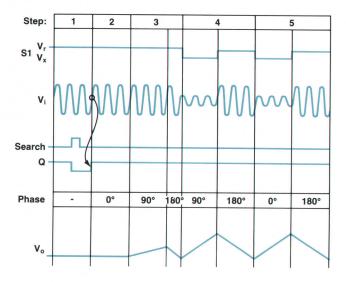

The 8182A has two logic analyzer modes of operation and a comparator mode. In the trigger start analyzer mode, after

Fig. 1. Simplified block diagram of the high-speed circuits of the 8182A Data Analyzer. New features are a programmable master clock delay and a real-time window comparison capability. recognizing a trigger condition, the 8182A begins to accept data into its high-speed memory. Stored data can be displayed as either state or timing diagrams, during or after completion of the measurement cycle. The microprocessor compares the received data with stored expected data and displays comparison failures on the state diagram or a concentrated overview in the error map.

In the trigger stop analyzer mode, after arming, the 8182A is always active, that is, it continually accepts data, filling and overwriting its high-speed memory. After recognition of a trigger event, it stops accepting data (after a selectable delay) and displays the previously stored data. Hence the events preceding and following the trigger event can be recorded. The monitoring capabilities are the same as in the trigger start analyzer mode.

The third mode, the trigger start compare mode, is an entirely new feature. It permits a real-time comparison of incoming data with a prestored data pattern contained in the high-speed memory. This comparison takes place during a time window synchronous with the clock input. The window is defined by a delay and a width. Every failure during the compare window generates a high logic level at a rear-panel output, and an error report can be displayed on the error map. Either one-shot or continuous cyclical measurements are possible.

#### **Hardware Architecture**

With the exception of the power supply, the display, and the microprocessor section, the 8182A hardware is to a high degree implemented with ECL to achieve 50-MHz operation and high timing accuracy. The eight-channel version of the 8182A contains two boards with digital control circuits, one board of clock generators, two boards containing the microprocessor and its interfacing, and two data boards, each with 4 channels. Six more data boards can be plugged into the remaining slots, extending the 8182A up to 32 channels. Fig. 1 shows a simplified block diagram of the hardware.

**Fig. 2.** High-impedance, high-frequency, dual-threshold probing is provided by a special thick-film hybrid probe circuit.

### What Is Window Comparison?

When the 8182A Data Analyzer is in either of its logic analyzer modes, performing like a conventional analyzer, it samples a data stream on a point-by-point basis. Whatever is present between two sampling events can be analyzed with the aid of a glitch detector, but it is impossible to determine whether a glitch appeared at the beginning or end of a sampling period. Similarly, determining the stability of a logic level during any part of the sampling period is also a problem.

How can the status of data on a microprocessor bus be determined during the period beginning 50 ns before and ending 10 ns after a clock edge?

When the 8182A is operating in its comparator mode, a periodic time window can be programmed. During this time, the incoming data can be compared with an internally stored pattern. The time window is synchronous with the clock connected to the 8182A clock probe.

The comparison circuit consists of an XOR gate in each channel, which compares the incoming data with a fixed data pattern. A pulse of the desired window width (60 ns in the example given here) is applied to the enable input of the gate (see Fig. 1).

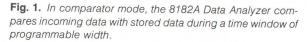

Fig. 2 shows the gate output. It is assumed that the stored data pattern consists of low levels, so an incoming high generates a positive pulse at the gate output while the window pulse is high. In Fig. 2a and 2b a failure is recognized. Fig. 2c and 2d are border-line. The compare error may not be recognized, although one

**Fig. 2.** Assuming that the stored data pattern consists of all low levels, an incoming high level during the window causes a positive compare result. Failures (a) and (b) are easily recognized, while cases (c) and (d) are borderline.

edge of the incoming data lies within the time window. At the 8182A input, the incoming data edge must be within 4 ns of the window edge for an error to be diagnosed correctly.

-Martin Dietze

#### **Active Probes and Input Amplifiers**

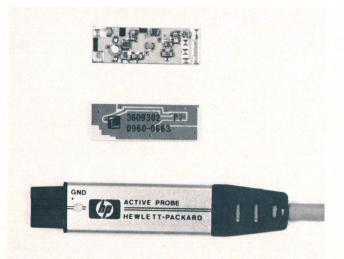

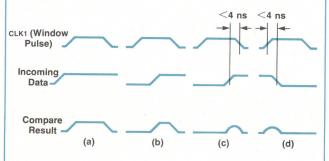

To achieve the design goals of high-impedance, lowcapacitance probing with high-frequency and dualthreshold capabilities, a special active probe circuit was developed. It is realized as a thick-film hybrid circuit (Fig. 2).

The dimensions of the hybrid are 29.7 mm  $\times$  10 mm  $\times$  2.4 mm. Special care had to be taken in designing the highimpedance input stage layout to achieve the small input capacitance of less than 7 pF (the hybrid alone has only a 4.5-pF input capacitance). The hybrid is packaged in a small aluminum case and connected to a special 1.5-m cable consisting of two shielded cables, one of which is 50 $\Omega$ coax, and two single wires for power and compensation for ground potential differences. Four of these active probes and cables share a single connector, which can be connected to the rear panel of the instrument.

Fig. 3 is a diagram of the active probe and input amplifier circuit. At the probe input, a spark gap (a laser-cut thick-film resistor) limits electrostatic discharge to several hundred volts. The input information  $V_{\rm IN}$  is divided into an ac path and a dc path. The ac signal is FET-buffered after frequency-compensated voltage division by 5 and sent to the analyzer by a line driver with a series termination. At the analyzer end of the cable, the signal is inverted.

The dc path is a simple op-amp circuit with a gain of -0.2. The input signal is level-shifted according to the threshold voltage so the high-speed comparator always compares its input signal with zero volts. Since the dc input is brought to the instrument at virtual ground, the input characteristics of the active probe remain constant with frequency. The capacitance of the line has no influence, and cable noise is significantly reduced.

After the incoming signal has been divided by 5 and shifted according to the programmed threshold, it is applied to a high-speed comparator, which has a few millivolts of hysteresis to suppress noise and high-frequency oscillation.

The 8182A is capable of comparing the incoming data with two thresholds simultaneously. For this, two neighboring channels are combined by relays in the following manner. The threshold comparator of one channel is disconnected from its input amplifier and connected to the amplifier of the other channel, so that the second channel sends its signal to two comparators. The first channel is then switched off. One comparator is used to compare the low-level threshold and the other to compare the high-level threshold. The data from both comparators is stored in two memory channels before the microprocessor combines them into one report. Eight channels can always be selected to perform dual-threshold measurements on four data inputs.

#### Data Sampling in the Logic Analyzer Modes

In the trigger start analyzer mode and the trigger stop analyzer mode, the data being digitized by the comparators is sampled in the sample flip-flop by the master clock (Fig. 1). The sample flip-flop is the heart of the analyzer. It has excellent sampling jitter characteristics (50 ps or less) and low temperature drift. The sampling jitter of a D-type flipflop is the time interval between the specified setup and hold times where the output is not defined.

Variable delay lines in the data channels are used to compensate for the clock circuit's propagation delay and the sampling flip-flop's setup and hold times (more about this later).

Fig. 3. Active probe circuit and analyzer input amplifier circuit.

The sampled data is written into the high-speed RAM by the gated write pulse generated by the trigger unit. The data can also be compared by the microprocessor with a fixed data pattern contained in the reference memory. A previously received data pattern contained in the high-speed RAM can be dumped into the reference memory. The reference memory can also be loaded and modified via the keyboard.

#### Interactive Read

A novel feature of the trigger start analyzer mode is the interactive read circuit. It permits the microprocessor to read the contents of the high-speed RAM cells during data sampling without losing data. This means that at a slow clock rate, the sampled data can be displayed immediately on the screen (e.g., on the timing diagram) after every sample. Therefore, it is unnecessary to wait until a measurement has been completed before seeing the result on the screen, unlike almost all other logic analyzers.

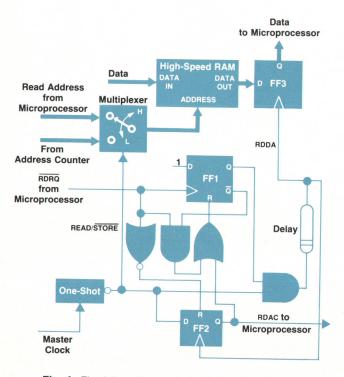

A special circuit to perform the difficult task of timing the interaction of the microprocessor and the asynchronous sampling was developed. A simplified diagram is shown in Fig. 4. A READ/STORE signal is generated from the master clock by a retriggerable monostable multivibrator (one-shot) and applied to an address multiplexer. For 50 ns after each positive transition of the master clock, the outputs of the high-speed address counter are tied to the RAM address inputs and a sampled word is stored. The multiplexer then applies the microprocessor-controlled read address to the RAM address inputs. If a read request (RDRQ) was initiated by the microprocessor, the circuit now starts reading the RAM contents at the read address. RDRQ is stored in FF1.

**Fig. 4.** The interactive read circuit lets the microprocessor read the contents of the high-speed RAM during data sampling without losing data.

**Fig. 5.** Clock timing circuits produce the programmable delay and the programmable width of the master clock.

The ANDing of the Q output of FF1 and READ/STORE generates a read data (RDDA) signal, storing the contents of the chosen RAM cell in FF3 after an appropriate delay (RAM access time). If this read activity is not interrupted by the next master clock, RDDA generates a read acknowledge (RDAC) signal, which informs the microprocessor that valid data has been stored in FF3, and FF1 is reset. Now the microprocessor can read the content of FF3 and initiate another read request.

If the read process has been interrupted by a new master clock, which has a higher priority, the multiplexer switches immediately to the address counter. Sampled data is then written into the RAM. Meanwhile, the RDDA signal is terminated and RDAC is suppressed. After the one-shot's period has elapsed, the signal RDDA is reinitiated. This process is repeated until the RAM has been successfully read.

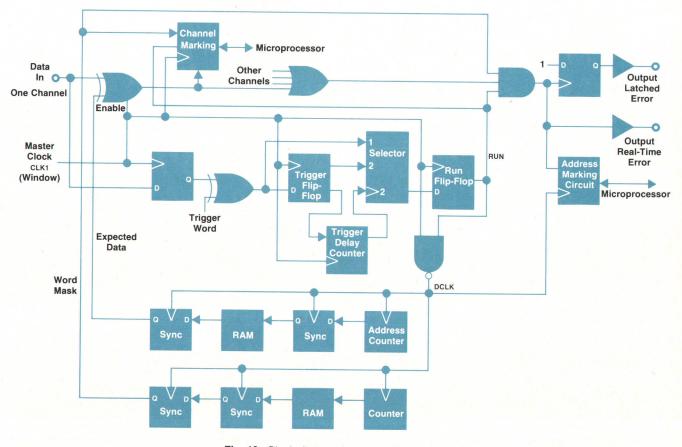

#### **Real-Time Comparison**

In the trigger start compare mode, the high-speed RAM is used to read out expected data in real time for comparison with incoming data. The same patterns are used in both logic analyzer and comparator modes. The high-speed RAM contents and the data from the active probes are sent simultaneously to the window comparators (see Fig. 1). There they are compared channel by channel during a time interval determined by the delay and width of the master clock. The compare results of all channels are then ORed. The output of the OR gate is qualified with a status signal and the word mask signal (discussed later). The result is immediately available at the rear-panel **PULSED ERROR** output. The result of every word comparison is stored in a special RAM that has one bit for each address. The contents of this RAM form the error map.

A second error output, **LATCHED ERROR**, is driven by a flip-flop that is set by the first error during a comparison sequence. This output remains high after the end of the measurement for further processing. It is reset when a new measurement is started. A character string in the display labeled Compare Failed/Passed shows the status of the latched error output.

Channels that have failed are marked on the displayed error page. To obtain this information, the output of every channel's window comparator is processed separately. The result of any real-time comparison is two-dimensional, with both faulty words (Y) and faulty channels (X) identified. To analyze any failures that are discovered, the logic analyzer modes can be used.

Sometimes there is no requirement to compare the results of all channels or all words. The 8182A is equipped with a means for disabling individual channels and inhibiting the compare results for individual words by setting them to "don't care." Individual words are inhibited by a separate word mask memory, running in parallel with the highspeed RAM. Its output is gated with the real-time compare result.

#### **Clock Timing**

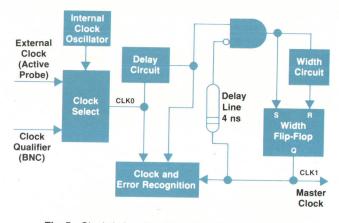

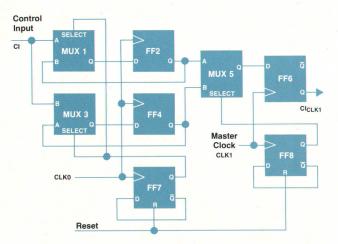

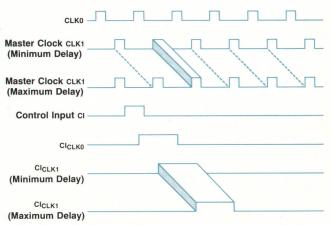

Clock timing circuits on the clock board produce the programmable delay and the programmable width of the master clock. A simplified diagram is shown in Fig. 5. The active clock CLK0 is a combination of the external or internal clock and the clock qualifier input.

The internal clock is generated by a 100-MHz oscillator, divided down in 1-2-5 steps. CLK0 triggers the delay circuit, which sets the width flip-flop, which is reset by the width circuit. The flip-flop output is the master clock, CLK1.

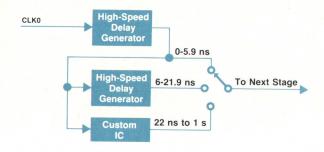

Delay and width generation is done mainly with custom ICs, as it is in the 8180A Data Generator (see Fig. 6). However, in the analyzer, it is of great importance to keep the

### **Generation of Analog Voltages**

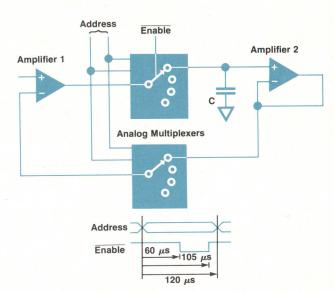

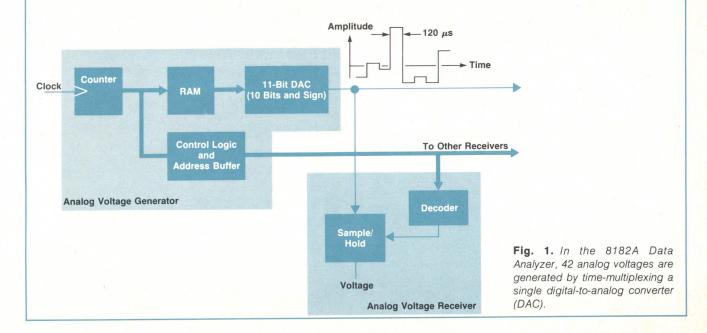

A multichannel instrument with universal features, working with several logic families, requires the ability to attach various programmable thresholds to different probes. In addition, features like delay and width, also programmed by analog voltages, are required. Therefore, many programmable voltages had to be made available in the 8182A Data Analyzer. The actual number is 42. These voltages are generated cyclically by a single digitalto-analog converter (DAC) and sent serially to all the places where they are required. On arrival, sample-and-hold circuits select the desired level at the desired time (see Fig. 1).

Addresses and logic control signals are generated by the counter. The RAM, which stores 11-bit words to be used in level generation, delivers information to the DAC for conversion. The dc levels are then passed to the sample-and-hold circuits, together with logic control signals and address information. Fig. 2 shows a simplified sample-and-hold circuit. Amplifier 1 charges the capacitor during the time that the enable signal is low, and amplifier 2 tracks that voltage. The feedback in the circuit eliminates the offset voltage of amplifier 2.

-Bernhard Roth

**Fig. 2.** Sample-and-hold circuits at various points in the analyzer select the correct analog voltage at the correct time.

**Fig. 6.** Custom ICs are used in the delay circuit (shown) and the similar width circuit. Special high-speed delay generators minimize the delay through the circuit.

fixed delay through the circuit to a minimum. The reason for this is that every data channel also has to be delayed to achieve the specified sampling accuracy. For this reason, special high-speed delay generators implemented with 100k ECL are used. These have a minimum fixed delay and a variation of up to 20 ns. A simplified circuit diagram is shown in Fig. 7.

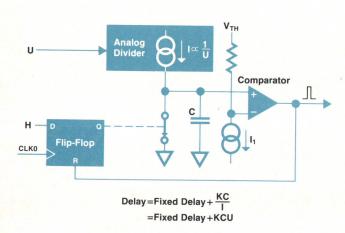

An incoming edge sets the flip-flop. Output Q opens the switch, forcing current I to charge capacitor C, creating a positive-going ramp. I is generated from the signal U by an analog divider. The instant the threshold voltage is reached, the flip-flop is reset and C is discharged. The pulse width at the output of the comparator is determined by the propagation delay through the components. The fixed delay is roughly 6 ns and the variable delay is proportional to U. Current  $I_1$  is used to improve linearity.

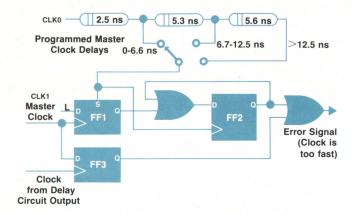

Since the main application of the data analyzer is in synchronous operation with programmed delay and/or width, constant observation of the external clock in relation to the actual delay and width is necessary to ensure that every active input clock edge creates a correct master clock pulse. When the time between two consecutive CLK0 pulses is too short to produce two correct master clock pulses, the operator is informed. This task is accomplished by an error recognition circuit (see Fig. 8).

Error recognition is performed along two paths. The first is FF1/FF2, and the second is FF3. The delayed CLK0 sets FF1 and samples FF1's output with FF2. The master clock

**Fig. 8.** An error recognition circuit signals the operator when the time between two consecutive active clock pulses is too short to produce two correct master clock pulses.

resets FF1, so that the whole process starts again. If two CLK0 pulses occur before a master clock edge, the second CLK0 pulse causes FF2's output to go high and hold that status. The delay circuit output samples the master clock with FF3. FF3's output goes high if the width circuit (see Fig. 5) is triggered too fast. If one of the paths recognizes that the clock is too fast, the corresponding message appears on the display and all flip-flops are reset by the microprocessor, which then continues to poll the error circuit.

The master clock is buffered and sent on five transmission lines of equal length from the motherboard to all data channels and control circuits.

#### Trigger Unit

Data

Triggering of the 8182A depends upon a combination of the states of the trigger arm input and the trigger qualifier, the appearance of the trigger word at the data inputs, and the state of the trigger event counter.

When the **RUN** key is pressed, the 8182A goes into the armed state and begins to search for trigger events. The trigger arm input is edge-triggered and serves as a preset input. The trigger qualifier and trigger word must be true at the same time to clock the trigger event counter, which runs in two modes:

RAM 2 Multiplexer **Glitch Detector off** RAM 3 0 Glitches **Glitch Detector on** Master Clock Shift Register **Glitch Detector off** 1 0 0 0 **Glitch Detector on** 1 0 0

Fig. 7. Simplified circuit diagram of the high-speed delay generator.

**Fig. 9.** For glitch detection, the high-speed RAM is split into data and glitch memories of equal size.

- 1. "Allow gaps yes." After the programmed number of true trigger events has been counted, the trigger event counter activates the trigger delay counter.

- 2. "Allow gaps no." Only true trigger events that occur one after the other at every master clock time are counted. If a false trigger event is recognized, the counter is reset to zero.

When all trigger conditions are true, the trigger delay counter, which consists of a count-down circuit that can be preset to any value between 0 and 65535, is started. When the delay counter has reached zero, the 8182A responds to the trigger condition. In the trigger start analyzer mode, it begins to write the incoming data into the high-speed RAM. In the trigger stop analyzer mode, it stops data recording. In the trigger start compare mode, it begins the comparison of incoming data. All trigger conditions can be set to "don't care," that is, they appear to be always true. The 8182A then starts immediately with the first incoming active clock edge. The instrument can also be started immediately by pressing the **SAMPLE** key, which overrides all trigger conditions and generates one clock pulse. Pressing the **SAMPLE** key repeatedly or holding it down generates additional clock pulses for storing or comparing data manually.

#### **Glitch Detectors**

Each channel of the 8182A has its own glitch detector. In contrast to the latch mode found in many analyzers, the glitch detector allows the 8182A to differentiate between a data transition and a glitch, which is defined as more than one data transition per sampling interval. To store the detected glitches in addition to the sampled data, the high-

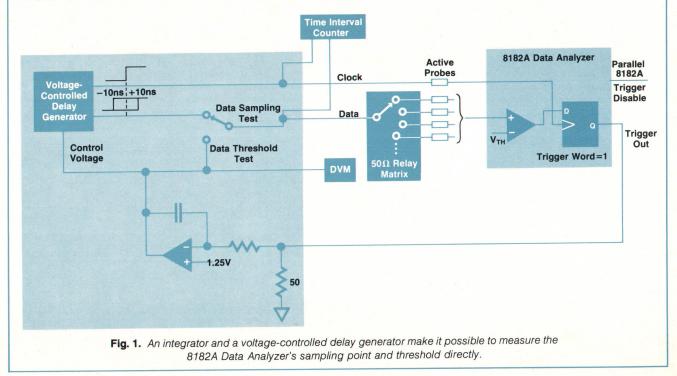

# Testing the Key Specifications of the 8182A

Since the 8182A is an analyzer, and key specifications such as sampling accuracy ( $\pm 1$  ns) and threshold accuracy ( $\pm 10$  mV) refer to inputs, direct measurement of these important values is extremely difficult. Instead, signals must be applied and conclusions drawn about the performance of the instrument from its response.

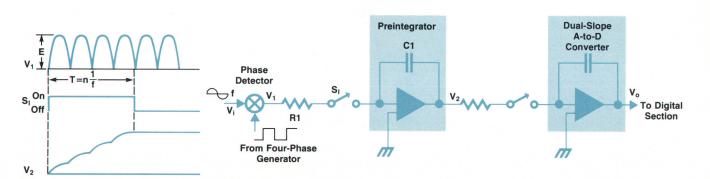

Fig. 1 illustrates a method by which it is possible to measure the actual sampling point and threshold directly. The heart of this test system is an electronic tool consisting of a simple integrating op-amp circuit and a voltage-controlled delay generator. The 8182A can be programmed and configured to appear as a voltage comparator followed by a D-type flip-flop. For this application, the 8182A can be considered as a level comparator for the

data inputs, and as a phase comparator for data inputs with reference to the clock input.

The closed loop consisting of the 8182A, integrator, and voltage-controlled delay generator provides a data slope at the active probe's input at the precise time of the actual sampling point. The measurement of the sampling point can now be performed simply by a time interval counter.

The threshold measurement is performed using the closed loop without the delay generator, thus passing the output of the integrator to the data inputs. The resulting voltage level is read with a DVM.

**Fig. 10.** This correlator circuit attaches the trigger control input sampled by CLK0 to the appropriate master clock (CLK1) pulse. Thus it prevents erroneous triggering resulting from the variable sampling point delay.

speed RAM is divided into data memory and glitch memory, each having a capacity of 512 bits per channel. Therefore, when the glitch detector is switched on, the memory capacity of each channel is halved.

Fig. 9 shows the organization of the high-speed RAM. Each channel stores its data in four  $256 \times 1$ -bit RAM arrays. The CS signals are provided by a shift register. When glitch detection is off, data is simultaneously switched by the multiplexer to each of the four RAM fields. The shift register is preloaded with (1,0,0,0). After 256 master clocks, the

Fig. 11. Timing diagram for the correlator circuit of Fig. 10.

contents of the shift register are advanced one cell to the right, resulting in (0,1,0,0). In this way, all four RAM arrays are enabled in sequence and filled with data. When glitch detection is on, the multiplexer separates the RAM inputs so that data goes to RAM arrays 1 and 2, and glitches to arrays 3 and 4. The shift register is then preloaded with (1,0,1,0). Thus, arrays 1 and 3 are enabled at the same time, with 2 and 4 following 256 clock pulses later.

The glitch detector used in the 8182A is a modified version of the well proven detector in the 1615A Logic Analyzer,<sup>1</sup> improved to perform at 50 MHz. In principle, the glitch detector consists of a pair of edge-triggered flip-flops (one for positive edges and one for negative edges) that

Fig. 12. Block diagram in logic analyzer modes. A multiphase clock system and data pipelining are used.

serve as pulse stretchers, lengthening every glitch so that it can be sampled by the master clock. To avoid dead times during resetting of the glitch detectors, each edge-triggered flip-flop is duplicated. While one pair of flip-flops is active to receive a glitch, the other is reset after its glitch information has been written into the glitch memory. Obviously, very careful design of the circuit and printed circuit board was necessary to achieve accurate 50-MHz operation.

#### **Control Input Correlators**

A special problem arose because of the programmable sampling point delay. With an increase in the sampling point delay, the relationship between the master clock and the initial CLK0 is modified, and this can result in erroneous triggering. To avoid this phenomenon, the sampling of the control inputs (clock qualifier, trigger arm, trigger qualifier, and external stop) is performed with the undelayed signal CLK0. This gives an exact specification of the control input's sampling point delay.

A correlator circuit (Fig. 10), has the task of attaching the control input sampled by CLK0 to the appropriate master clock (CLK1) pulse. This task could have been performed by programmable delay lines, but the 8182A uses a simpler way, a digital circuit that adapts automatically to different delay settings.

The key idea is to store the sampling result of clock phase CLK0 in two input registers for two clock periods, each with one clock period offset.

The output register takes the appropriate information

from the input registers via a multiplexer, which is clocked by the delayed clock phase CLK1. The whole process is controlled by flip-flops FF7 and FF8, which have to be initialized correctly to maintain the phase relationships.

The minimum propagation delay time between CLK0 and CLK1 is 10 ns (with CLK1 programmed to 0 ns added delay), which is equal to the maximum allowable propagation delay for FF2 and multiplexer MUX5 and the setup time of FF6. If the CLK1 delay is increased to more than one clock period, no problem arises.

Fig. 11 is a timing diagram for the correlator circuit, Fig. 10.

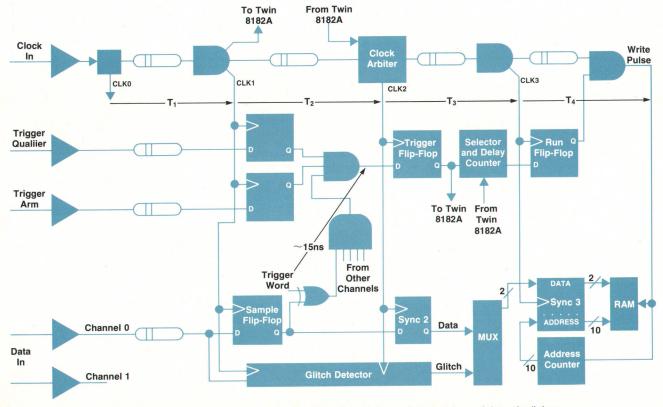

#### Time Relationships in the Logic Analyzer Modes

In the logic analyzer modes (i.e., trigger start analyzer and trigger stop analyzer modes), a multiphase clock system and data pipelining are used (see Fig. 12). The clock phases are derived from CLK0 via delay lines. The multiphase system makes it possible to sample, trigger, and store data on the same clock pulse. Data is sampled on transitions of the master clock CLK1, which can be delayed relative to the clock input. The sampled data is captured by SYNC2. The trigger word is detected simultaneously and stored by the trigger flip-flop at clock phase CLK2. The trigger information is fed through a selector to the run flip-flop. Data and memory addresses are sampled by CLK3. With the run flipflop active, write pulses are supplied and data is written into the high-speed RAM. Memory addresses are supplied by the address counter, which is incremented by the write

Fig. 13. Block diagram in comparator mode.

pulses.

Since the maximum sampling rate is 50 MHz (20 ns period), the clock phases must be within 20 ns of each other to achieve synchronous operation. On the other hand, the propagation delay of the trigger word is roughly 15 ns because of some gating operations and the motherboard connections. In the twin or parallel operating mode, trigger information sent to and received from the second 8182A via a twisted-pair cable takes about 12 ns excluding gate propagation delays. With these values in mind, the timing of clock phases CLK1 to CLK2 and CLK2 to CLK3 becomes rather critical. Therefore, delay times T2 and T3 are adjusted individually to 18 ns. To allow for the data and address setup time specifications and the write pulse width delay of the high-speed RAM, T4 is set at 7 ns and the write pulse width is 7 ns.

#### **Timing in the Comparator Mode**

The timing system for the comparator mode (i.e., the trigger start compare mode) is somewhat different from the logic analyzer modes because data is not sampled and written into memory. Instead, incoming data is compared in real time with data read from the high-speed memory. The compare result cannot be pipelined because of its analog character. Unfortunately, trigger word detection and processing takes time, as it does in the logic analyzer modes. To avoid a trigger delay that is a function of frequency, the clock inputs of the trigger and run flip-flops are modified to be synchronous with clock phase CLK1. This results in a fixed minimum trigger delay of 1 clock period. In twin operation, the minimum trigger delay is increased to two clock periods.

Fig. 13 is a block diagram of the instrument in comparator mode. After the run flip-flop is triggered, a clock pulse

### **Interfacing the Device Under Test**

Multichannel instruments with high-frequency capabilities such as the 8180A Data Generator and the 8182A Data Analyzer require special attention to the problem of DUT interfacing.

The design goals were easy adaptability, good signal performance, universal interface capabilities, and suitability for all generator and analyzer requirements.

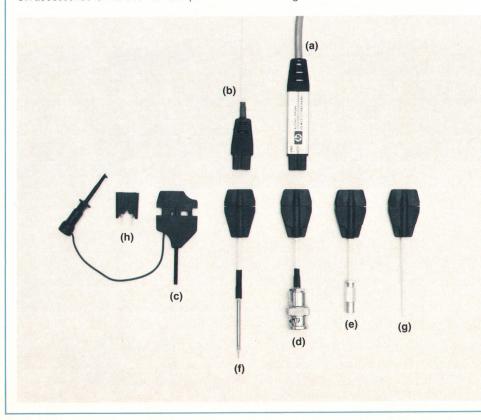

A special connector is located at the front end of the analyzer active probe (see Fig. 1a). At the generator end, the same connector type is molded directly onto a  $50\Omega$  coaxial cable (Fig. 1b). Six accessories for various interface possibilities were designed:

- Grabber with ground lead (Fig. 1c)

- BNC adapter (Fig. 1d)

- SMB adapter (Fig. 1e)

- Adapter for the HP 10024A IC Test Clip (Fig. 1f)

- Open-ended adapter for a custom connector or fixed wiring (Fig. 1g)

- Solder-in receptacles for printed-circuit boards (Fig. 1h).

-Horst Link

**Fig. 1.** 8182A Data Analyzer active probe and accessories.

Fig. 14. In parallel or twin operation of two 8182A Data Analyzers, clock arbiter circuits synchronize the two units in the logic analyzer modes. In comparator mode, the arbiters are not used.

(DCLK) is generated at the end of the time window signal (CLK1). This prepares the next data word for comparison, supplies the next address to the RAM, and increments the address counter and the word masking circuit, which provides for the masking of errors at every user-selectable address. The compare result of every word is stored by the address marking circuit. The channel marking circuit pinpoints the channel or channels in which a compare failure has occurred. Interrogation of the address marking and channel marking circuits gives the microprocessor the information required to generate the error map.

#### **Parallel Operation**

The 8182A is designed to run with another 8182A in parallel. This configuration increases the number of channels up to maximum of 64. For this purpose, both instruments are tied together with a multiple-conductor cable which synchronizes the trigger conditions. The clock probes of both instruments are connected to the same external clock source to maintain high sampling accuracy and low skew.

The user must ensure that both instruments are programmed compatibly. Parameters such as trigger conditions, sampling point delay, and thresholds are individually programmable for both instruments. The trigger delay counters of both instruments can be programmed independently. Hence the start of one 8182A can be delayed with respect to the other for a defined number of clock periods.

The clock arbiter synchronizes clock phases CLK2 and CLK3 of both 8182As in the logic analyzer modes. The

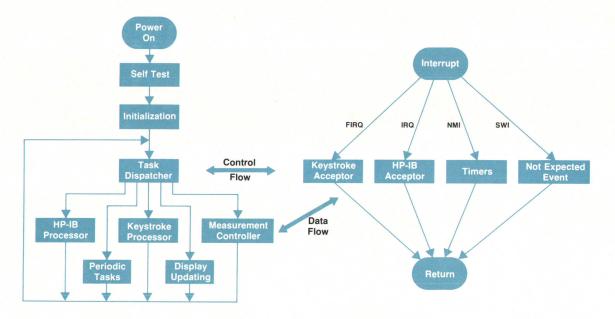

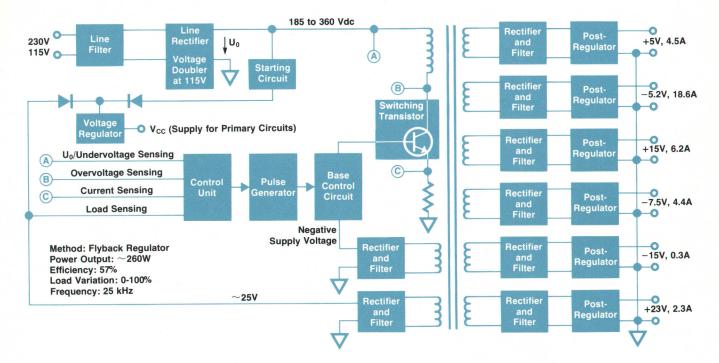

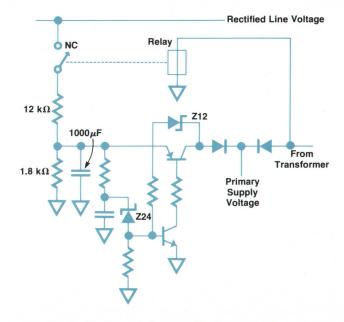

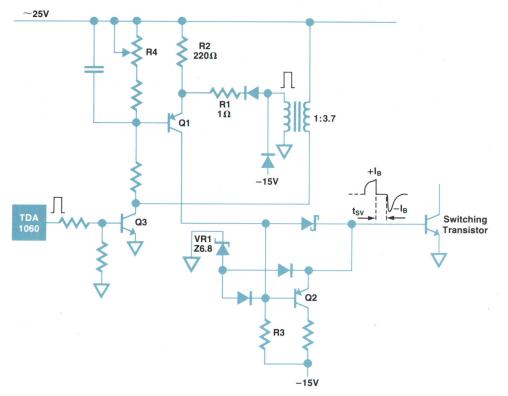

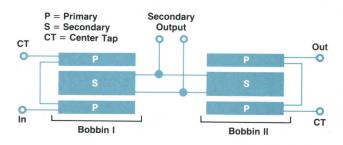

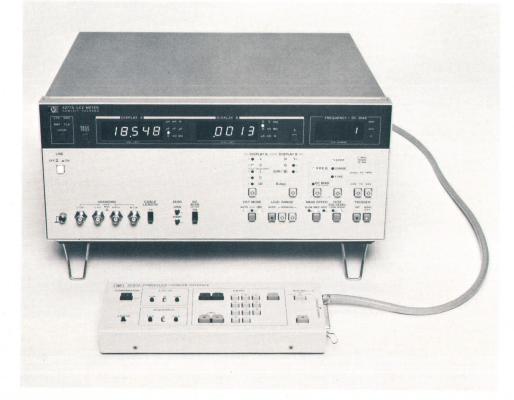

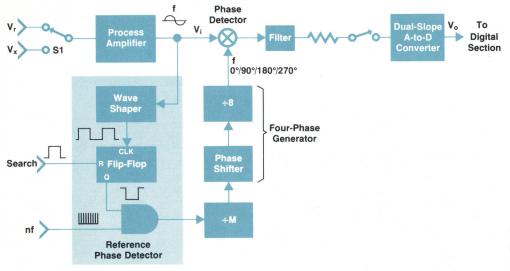

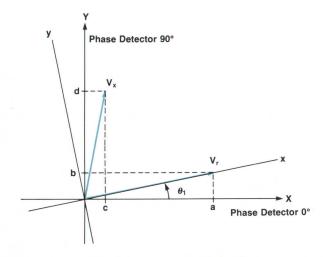

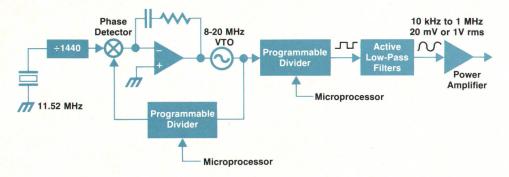

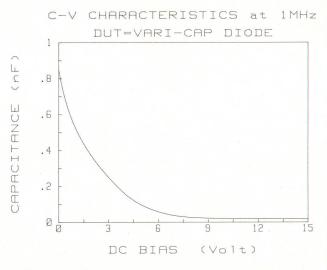

arbiter output pulse (CLK2) is delayed by 18 ns with respect to whichever CLK1 has the greatest delay (see Fig. 14). Basically, the circuit consists of two high-speed 100k ECL D-type flip-flops. The first is tied to internal clock phase CLK1 by a compensating delay line, and the second is tied to CLK1 of the second 8182A. An output pulse, whose width is determined by propagation delay feedback, is generated when the second flip-flop is clocked. Clock phases CLK2 of both 8182As then have the same delay with respect to the incoming clock within a few hundred picoseconds, the sampling point delays being different.